# Code Generation for Data Processing

Lecture 1: Introduction and Interpretation

#### Alexis Engelke

Chair of Data Science and Engineering (125) School of Computation, Information, and Technology Technical University of Munich

Winter 2022/23

## Module "Code Generation for Data Processing"

### Learning Goals

- ▶ Getting from an intermediate code representation to machine code

- Designing and implementing IRs and machine code generators

- ► Apply for: JIT compilation, query compilation, ISA emulation

### Prerequisites

Computer Architecture, Assembly

ERA, GRA/ASP

► Databases, Relational Algebra

GDB

▶ Beneficial: Compiler Construction, Modern DBs

### Topic Overview

#### Introduction

- ► Introduction and Interpretation

- Compiler Front-end

### Intermediate Representations

- ► IR Concepts and Design

- ► LLVM-IR

- LLVM Transforms and Analyses

### Compiler Back-end

- ► Instruction Selection

- Register Allocation

- Linker, Loader, Debuginfo

### **Applications**

- JIT-compilation + Sandboxing

- Query Compilation

- ► Binary Translation

3

### Lecture Organization

- ► Lecturer: Dr. Alexis Engelke engelke@in.tum.de

- ► Time slot: Thu 10-14, 02.11.018

- ▶ Material: https://db.in.tum.de/teaching/ws2223/codegen/

#### Exam

- Written exam, 90 minutes, no retake, date TBD

- ► (Might change to oral on very low registration count)

#### Exercises

- Weekly homework, often with programming exercise

- ► Submission via e-mail: engelke+cghomework@in.tum.de

- Probably no explicit grading, feedback on best effort

- Exercise sessions to present and discuss solutions

#### Grade Bonus

- ▶ Requirement: N-2 "sufficiently working" homework submissions and at least 2 presentations of homework in class

- ▶ Bonus: grades in [1.3; 4.0] improved by 0.3

### Why study compilers?

- Critical component of every system, functionality and performance

- ► Compiler mostly *alone* responsible for using hardware well

- Brings together many aspects of CS:

- ► Theory, algorithms, systems, architecture, software engineering, (ML)

- New developments/requirements pose new challenges

- ▶ New architectures, environments, language concepts, . . .

- High complexity!

### Compiler Lectures @ TUM

Compiler Construction IN2227, SS. THEO

Front-end, parsing, semantic analyses, types

Program Optimization IN2053. WS. THEO

Analyses, transformations, abstract interpretation

Virtual Machines IN2040, SS. THEO

Mapping programming paradigms to IR/bytecode

Programming Languages CIT3230000, WS

Implementation of advanced language features

Code Generation CIT3230001, WS

Back-end, machine code generation, JIT comp.

### Why study code generation?

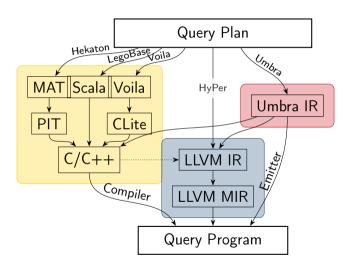

- ► Frameworks (LLVM, ...) exist and are comparably good, but often not good enough (performance, features)

- Many systems with code gen. have their own back-end

- ► E.g.: V8, WebKit FTL, .NET RyuJIT, GHC, Zig, QEMU, Umbra, . . .

- ► Machine code is not the only target: bytecode

- Often used for code execution

- ► E.g.: V8, Java, .NET MSIL, BEAM (Erlang), Python, MonetDB, eBPF, ...

- Allows for flexible design

- ▶ But: efficient execution needs machine code generation

### Proebsting's Law

"Compiler advances double computing power every 18 years."

- Todd Proebsting, 1998<sup>1</sup>

▶ Still optimistic; depends on number of abstractions

### Motivational Example: Brainfuck

- Turing-complete esoteric programming language, 8 operations

- ► Input/output: . ,

- Moving pointer over infinite array: < >

- ► Increment/decrement: + -

- ▶ Jump to matching bracket if (not) zero: []

► Execution with pen/paper? ∴

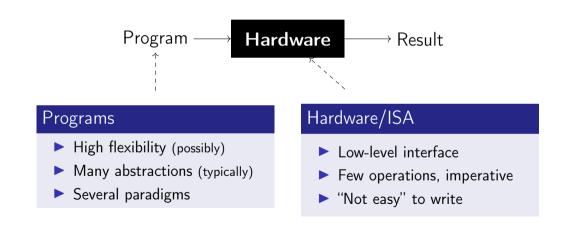

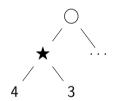

### Program Execution

### Motivational Example: Brainfuck – Interpretation

Write an interpreter!

```

unsigned char state[10000];

unsigned ptr = 0, pc = 0;

while (prog[pc])

switch (prog[pc++]) {

case '.': putchar(state[ptr]); break;

case ',': state[ptr] = getchar(); break;

case '>': ptr++; break;

case '<': ptr--; break;

case '+': state[ptr]++; break;

case '-': state[ptr]--; break;

case '[': state[ptr] || (pc = matchParen(pc, prog)); break;

case ']': state[ptr] && (pc = matchParen(pc, prog)); break;

}

```

### Program Execution

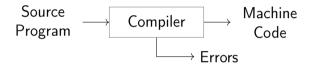

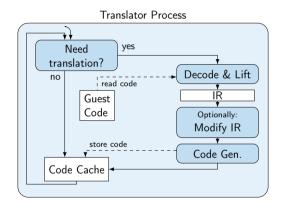

### Compiler

$\mathsf{Program} \to \mathsf{Compiler} \quad \to \mathsf{Program}$

- ► Translate program to other lang.

- Might optimize/improve program

- ightharpoonup C, C++, Rust ightarrow machine code

- ightharpoonup Python, Java ightharpoonup bytecode

#### Interpreter

$\mathsf{Program} \to \mathsf{Interpreter} \ \longmapsto \mathsf{Result}$

- Directly execute program

- ► Computes program result

- Shell scripts, Python bytecode, machine code (conceptually)

Multiple compilation steps can precede the "final interpretation"

### Compilers

- ► Targets: machine code, bytecode, or other source language

- ► Typical goals: better language usability and performance

- ► Make lang. usable at all, faster, use less resources, etc.

- ► Constraints: specs, resources (comp.-time, etc.), requirements (perf., etc.)

- **Examples**:

- ► "Classic" compilers source → machine code

- ▶ JIT compilation of JavaScript, WebAssembly, Java bytecode, . . .

- Database query compilation

- ► ISA emulation/binary translation

### Compiler Structure: Monolithic

► Inflexible architecture, hard to retarget

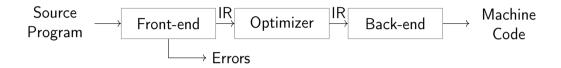

# Compiler Structure: Two-phase architecture

#### Front-end

- Parses source code

- Detect syntax/semantical errors

- ► Emit *intermediate representation* encode semantics/knowledge

- ▶ Typically:  $\mathcal{O}(n)$  or  $\mathcal{O}(n \log n)$

#### Back-end

- ► Translate IR to target architecture

- ► Can assume valid IR (~ no errors)

- Possibly one back-end per arch.

- ightharpoonup Contains  $\mathcal{NP}$ -complete problems

## Compiler Structure: Three-phase architecture

- Optimizer: analyze/transform/rewrite program inside IR

- Conceptual architecture: real compilers typically much more complex

- Several IRs in front-end and back-end, optimizations on different IRs

- ► Multiple front-ends for different languages

- Multiple back-ends for different architectures

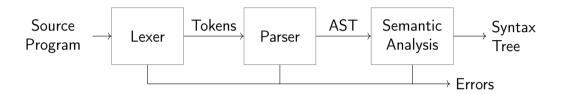

### Compiler Front-end

1. Tokenizer: recognize words, numbers, operators, etc.

$\mathcal{R}e$

- ightharpoonup Example: a+b\*c ightharpoonup ID(a) PLUS ID(b) TIMES ID(c)

- 2. Parser: build (abstract) syntax tree, check for syntax errors

$\mathcal{CFG}$

- ➤ Syntax Tree: describe grammatical structure of complete program Example: expr("a", op("+"), expr("b", op("\*"), expr("c"))

- ► Abstract Syntax Tree: only relevant information, more concise Example: plus("a", times("b", "c"))

- 3. Semantic Analysis: check types, variable existence, etc.

- 4. IR Generator: produce IR for next stage

- ► This might be the AST itself

### Compiler Back-end

- 1. Instruction Selection: map IR operations to target instructions

- ▶ Use target features: special insts., addressing modes, . . .

- Still using virtual/unlimited registers

- 2. Instruction Scheduling: optimize order for target arch.

- Start memory/high-latency earlier, etc.

- Requires knowledge about micro-architecture

- 3. Register Allocation: map values to fixed register set/stack

- ▶ Use available registers effectively, minimize stack usage

# Motivational Example: Brainfuck - Front-end

- ► Need to skip comments

- ► Bracket searching is expensive/redundant

- ► Idea: "parse" program!

- ► Tokenizer: yield next operation, skipping comments

- ▶ Parser: find matching brackets, construct AST

### Motivational Example: Brainfuck – AST Interpretation

► AST can be interpreted recursively

```

struct node { char kind; int cldCnt; struct node* cld; };

struct state { unsigned char* arr; size_t ptr; };

void donode(struct node* n, struct state* s) {

switch (n->kind) {

case '+': s->arr[s->ptr]++; break;

// ...

case '[': while (s->arr[s->ptr]) children(n); break;

case 0: children(n); break; // root

void children(struct node* n, struct state* s) {

for (int i = 0; i < n > cldCnt; i++) donode(n > cld + i, s);

```

### Motivational Example: Brainfuck – Optimization

- ► Inefficient sequences of +/-/</> can be combined

- ► Trivially done when generating IR

- Fold patterns into more high-level operations

- ► [-] = set zero

- [>] = find next zero (memchr)

- ► [->+>+«] = add to next two siblings, set zero

- ► [->+++<] = add 3 times to next sibling, set zero

- **.**...

### Motivational Example: Brainfuck – Optimization

- Fold offset into operation

- ▶ right(2) add(1) = addoff(2, 1) right(2)

- Also possible with loops

- Analysis: does loop move pointer?

- Loops that keep position intact allow more optimizations

- Maybe distinguish "regular loops" from arbitrary loops?

- ► Get rid of all "effect-less" pointer movements

- Combine arithmetic operations, disambiguate addresses, etc.

### Motivational Example: Brainfuck – Bytecode

- ► Tree is nice, but rather inefficient → flat and compact bytecode

- Avoid pointer dereferences/indirections; keep code size small

- ▶ Superinstructions: combine common sequences to one instruction

- Maybe dispatch two instructions at once?

- switch (ops[pc] | ops[pc+1] « 8)

### Motivational Example: Brainfuck - Threaded Interpretation

- ► Simple switch—case dispatch has lots of branch misses

- ► Threaded interpretation: at end of a handler, jump to next op

```

struct op { char op; char data; };

struct state { unsigned char* arr; size_t ptr; };

void threadedInterp(struct op* ops, struct state* s) {

static const void* table[] = { &&CASE ADD, &&CASE RIGHT, };

#define DISPATCH do { goto *table[(++pc)->op]; } while (0)

struct op* pc = ops;

DISPATCH:

CASE_ADD: s->arr[s->ptr] += pc->data; DISPATCH;

CASE_RIGHT: s->arr += pc->data; DISPATCH;

```

### Fast Interpretation

- Key technique to "avoid" compilation to machine code

- Preprocess program into efficiently executable bytecode

- Easily identifiable opcode, homogeneous structure

- ► Can be linear (fast to execute), but trees also work

- Perhaps optimize if it's worth the benefit

- ► Fold constants, combine instructions, ...

- Consider superinstructions for common sequences

- For very cold code: avoid transformations at all

- Use threaded-interpretation to avoid branch misses

### Compiler: Surrounding – Compile-time

► Typical environment for a C/C++ compiler:

- ► Calling Convention: interface with other objects/libraries

- Build systems, dependencies, debuggers, etc.

- Compilation target machine (hardware, VM, etc.)

### Compiler: Surrounding – Run-time

- ► OS interface (I/O, ...)

- ► Memory management (allocation, GC, ...)

- Parallelization, threads, . . .

- ▶ VM for execution of virtual assembly (JVM, ...)

- Run-time type checking

- Error handling: exception unwinding, assertions, . . .

- Reflection, RTTI

### Motivational Example: Brainfuck – Runtime Environment

- ► Needs I/O for . and ,

- Memory management: infinitely sized array

- ► Allocate on demand (easy?)

- What if main memory or address space is insufficient?

- Deallocation of empty pages?

- Error handling: unmatched brackets

## Compilation point: AoT vs. JIT

#### Ahead-of-Time (AoT)

- All code has to be compiled

- No dynamic optimizations

- Compilation-time secondary concern

#### Just-in-Time (JIT)

- Compilation-time is critical

- Code can be compiled on-demand

- Incremental optimization, too

- ► Handle cold code fast

- Dynamic specializations possible

- ► Allows for eval()

Various hybrid combinations possible

### Compiler Design: Effect of Languages – Imperative

- Step-by-step execution of program modification of state

- Close to hardware execution model

- Direct influence of result.

- ► Tracking of state is complex

- Dynamic typing: more complexity

- Limits optimization possibilities

```

void addvec(int* a, const int* b) {

for (unsigned i = 0; i < 4; i++)

a[i] += b[i]; // vectorizable?

}</pre>

```

```

func:

mov [rdi], rsi

mov [rdi+8], rdx

mov [rdi], 0 // redundant?

ret

```

# Compiler Design: Effect of Languages – Declarative

- Describes execution target

- Compiler has to derive good mapping to imperative hardware

- Allows for more optimizations

- Mapping to hardware non-trivial

- Might need more stages

- Preserve semantic info for opt!

- ► Programmer has less "control"

### Introduction and Interpretation – Summary

- ► Compilation vs. interpretation and combinations

- Compilers are key to usable/performant languages

- ► Target language typically machine code or bytecode

- Three-phase architecture widely used

- Interpretation techniques: bytecode, threaded interpretation, . . .

- JIT compilation imposes different constraints

### Introduction and Interpretation – Questions

- What is typically compiled and what is interpreted? Why?

- PostScript, C, JavaScript, HTML, SQL

- What are typical types of output languages of compilers?

- How does a compiler IR differ from the source input?

- What is the impact of the language paradigm on optimizations?

- What are important factors for an efficient interpreter?

- ▶ What are key differences between AoT and JIT compilation?

# Code Generation for Data Processing Lecture 2: Compiler Front-end

#### Alexis Engelke

Chair of Data Science and Engineering (125) School of Computation, Information, and Technology Technical University of Munich

Winter 2022/23

### Compiler Front-end

- ▶ Typical architecture: separate lexer, parser, and context analysis

- Allows for more efficient lexical analysis

- Smaller components, easier to understand, etc.

- ► Some languages: preprocessor and macro expansion

#### Lexer

- Convert stream of chars to stream of words (tokens)

- Detect/classify identifiers, numbers, operators, . . .

- ► Strip whitespace, comments, etc.

$$a+b*c \rightarrow ID(a)$$

PLUS ID(b) TIMES ID(c)

► Typically representable as regular expressions

# Typical Token Kinds

Punctuators

()[]{};=++=|||

Identifiers

abc123 main

Keywords

void int \_\_asm\_\_

Numeric constants

123 Oxab1 5.7e3 Ox1.8p1

Char constants

'a' u'œ'

String literals

$abc\x12\n$

Internal

- EOF COMMENT UNKNOWN INDENT DEDENT

- ► Comments might be useful for annotations, e.g. // fallthrough

### Lexer Implementation

```

def nextToken(inp: str) -> tuple[str, str, str]:

# Get next token, return (kind, value, remainder)

inp = inp.lstrip()

if not inp:

return "EOF", "", inp

if inp[0].isdigit():

m = re.match(r'[1-9][0-9]*|0([0-7]+|x[0-9a-fA-F]+|)', inp)

return "NUM", m[0], inp[m.end():]

if inp[0].isalpha():

m = re.match(r, [a-zA-Z] [a-zA-Z0-9]*, inp)

if m[0] in KEYWORDS: return m[0], m[0], inp[m.end():]

return "IDENT", m[0], inp[m.end():]

if inp[:2] == "+=": return "PLUSEQ", inp[:2], inp[2:]

if inp[:1] == "+": return "PLUS", inp[:1], inp[1:]

. . .

raise Exception()

```

# Lexing C??=

```

main() <%

// yay, this is C99??/

puts("hi_world!");

puts("what's_up??!");

%>

```

Output: what's up |

- ► Trigraphs for systems with more limited encodings/char sets

- Digraphs to provide a more readable alternative...

### Lexer Implementation

- Essentially a DFA (for most languages)

- ightharpoonup Set of regexes ightharpoonup NFA ightharpoonup DFA

- Respect whitespace/separators for operators, e.g. + and +=

- ► Automatic tools (e.g., flex) exist; most compilers do their own

- Keywords typically parsed as identifiers first

- ► Check identifier if it is a keyword; can use perfect hashing

- Other practical problems

- ▶ UTF-8 homoglyphs; trigraphs; pre-processing directives

### Parsing

- Convert stream of tokens into (abstract) syntax tree

- ► Most programming languages are context-sensitive

- ► Variable declarations, argument count, type match, etc.

- $\leadsto$  separated into semantic analysis

- Syntactically valid: void foo = doesntExist / "abc";

- Grammar usually specified as CFG

# Context-Free Grammar (CFG)

- ► Terminals: basic symbols/tokens

- ► Non-terminals: syntactic variables

- Start symbol: non-terminal defining language

- ightharpoonup Productions: non-terminal ightarrow series of (non-)terminals

```

stmt \rightarrow whileStmt \mid breakStmt \mid exprStmt

whileStmt \rightarrow while (expr) stmt

breakStmt \rightarrow break ;

exprStmt \rightarrow expr ;

expr \rightarrow expr + expr \mid expr * expr \mid expr = expr \mid (expr) \mid number

```

### Hand-written Parsing – First Try

- ► One function per non-terminal

- Check expected structure

- Return AST node

- Need look-ahead!

```

def parseBreakStmt(...):

matchToken("break")

matchToken("SEMICOLON")

return ("breakStmt".)

def parseWhileStmt(...):

matchToken("while")

matchToken("LPAREN")

expr = parseExpr(...)

matchToken("RPAREN")

stmt = parseStmt(...)

return ("whileStmt", expr, stmt)

def parseStmt(...):

# whoops!

```

## Hand-written Parsing – Second Try

- Need look-ahead to distinguish production rules

- Consequences for grammar:

- ► No left-recursion

- First *n* terminals must allow distinguishing rules

- LL(n) grammar; n typically 1

- ⇒ Not all CFGs (easily) parseable (but most programming langs. are)

- ► Now... expressions

```

def parseBreakStmt(...):

... # as before

def parseWhileStmt(...):

... # as before

def parseStmt(...):

tok = peekToken()

if tok == "break":

return parseBreakStmt(...)

if tok == "while":

return parseWhileStmt(...)

expr = parseExpr(...)

matchToken("SEMICOLON")

return ("exprStmt", expr)

```

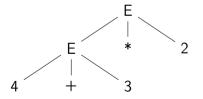

# **Ambiguity**

$$expr \rightarrow expr + expr \mid expr * expr \mid expr = expr \mid$$

(  $expr$  ) | number Input:  $4 + 3 * 2$

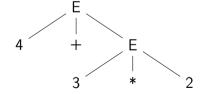

## Ambiguity – Rewrite Grammar?

$$primary \rightarrow (expr) \mid number$$

$expr \rightarrow primary + expr \mid primary * expr \mid primary = expr \mid primary$

$lnput: 4 + 3 * 2$   $lnput: 4 * 3 + 2$

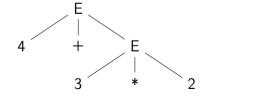

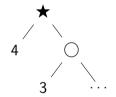

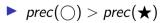

# Ambiguity – Precedence

Input: 4 ★ 3 ○ . . .

► Equal prec. and ★ is right-associative

- ▶  $prec(\bigcirc) < prec(★)$

- ► Equal prec. and ★ is left-associative

# Hand-written Parsing – Expression Parsing

- ► Start with basic expr.:

- Number, variable, etc.

- Parenthesized expr.

- Parse full expression

- Next token must be )

- Unary expr: followed by expr. with higher prec.

- < unary < []/->

```

def parsePrimaryExpr(...):

# handle numbers, unary operators,

# variables, parenthesized expr.

... # trivial ;)

def parseExpr(..., minPrec=0):

lhs = parsePrimaryExpr(...)

... # (next slide)

```

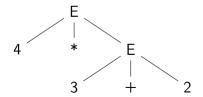

# Hand-written Parsing – Expression Parsing

- Only allow ops. with higher prec. on the right child

- Operator precedence

- $\blacktriangleright$  \*  $\rightarrow$  (3, left-assoc)

- ightharpoonup +

ightharpoonup (2, left-assoc)

- $ightharpoonup = \rightarrow (1, right-assoc)$

- ► Right-assoc.: allow same prec.

- Assignment, ternary

```

def parsePrimaryExpr(...):

# handle numbers, unary operators,

# variables, parenthesized expr.

... # trivial :)

def parseExpr(..., minPrec=0):

lhs = parsePrimaryExpr(...)

while True:

tok = nextToken()

prec, rassoc = OPERATORS[tok]

if prec < minPrec:</pre>

return lhs

# XXX: handling for: (, [, ?:

newPrec = prec if rassoc else prec+1

rhs = parseExpr(..., newPrec)

lhs = ("expr", tok, lhs, rhs)

```

## Hand-written Parsing – Expression Parsing

```

OPERATORS = {

"*": (3, False),

"+": (2, False),

"=": (1, True),

}

```

```

def parsePrimaryExpr(...):

# handle numbers, unary operators,

# variables, parenthesized expr.

... # trivial :)

def parseExpr(..., minPrec=0):

lhs = parsePrimaryExpr(...)

while True:

tok = nextToken()

prec, rassoc = OPERATORS[tok]

if prec < minPrec:</pre>

return lhs

# XXX: handling for: (, [, ?:

newPrec = prec if rassoc else prec+1

rhs = parseExpr(..., newPrec)

lhs = ("expr", tok, lhs, rhs)

```

# Top-down vs. Bottom-up Parsing

#### Top-down Parsing

- Start with top rule

- Every step: choose expansion

- ► LL(1) parser

- Left-to-right, Leftmost Derivation

- "Easily" writable by hand

- Error handling rather simple

- ► Covers many prog. languages

#### Bottom-up Parsing

- ► Start with text

- Reduce to non-terminal

- ► LR(1) parser

- ► Left-to-right, Rightmost Derivation

- Strict super-set of LL(1)

- Often: uses parser generator

- Error handling more complex

- Covers nearly all prog. languages

#### Parser Generators

- Writing parsers by hand can be large effort

- ▶ Parser generators can simplify parser writing a lot

- ► Yacc/Bison, PLY, ANTLR, ...

- Automatic generation of parser/parsing tables from CFG

- ▶ But: lexer often written by hand either way

- Used heavily in practice

#### Bison Example - part 1

```

%define api.pure full

%define api.value.type {ASTNode*}

%param { Lexer* lexer }

%code{

static int yylex(ASTNode ** lvalp, Lexer* lexer);

%token NUMBER

%token WHILE "while"

%token BREAK "break"

// precedence and associativity

%right '='

%left '+'

%left '*'

%%

```

### Bison Example – part 2

```

%%

stmt : WHILE '(' expr ')' stmt { $$ = mkNode(WHILE, $1, $2); }

| BREAK ':'

{ $$ = mkNode(BREAK, NULL, NULL); }

\{ \$\$ = \$1; \}

expr ';'

\{ \$\$ = mkNode('+', \$1, \$2); \}

expr : expr '+' expr

| expr '*' expr

\{ \$\$ = mkNode('*', \$1, \$2); \}

expr '=' expr

\{ \$\$ = mkNode('=', \$1, \$2); \}

| '(' expr ')'

\{ \$\$ = \$1; \}

I NUMBER

%%

static int yvlex(ASTNode** lvalp, Lexer* lexer) {

/* return next token, or YYEOF/... */ }

```

#### Parsing in Practice

- ➤ Some use parser generators, e.g. Python some use hand-written parsers, e.g. GCC, Clang

- Optimization of grammar for performance

- Rewrite rules to reduce states, etc.

- Useful error-handling: complex!

- Try skipping to next separator, e.g.; or,

- Programming languages are not always context-free

- C: foo\* bar;

- May need to break separation between lexer and parser

# Parsing C++

- ► C++ is not context-free (inherited from C): T \* a;

- ► C++ is ambiguous: Type (a), b;

- Can be a declaration or a comma expression

- ► C++ templates are Turing-complete<sup>2</sup>

- ► C++ parsing is hence undecidable<sup>3</sup>

- ► Template instantiation combined with C T \* a ambiguity

<sup>&</sup>lt;sup>2</sup>TL Veldhuizen. C++ templates are Turing complete. 2003. ⊚.

<sup>&</sup>lt;sup>3</sup>J Haberman. Parsing C++ is literally undecidable. 2013. ⊚.

## Semantic Analysis

- Needs context-sensitive analysis:

- ► Variable existence, storage, accessibility, . . .

- Function existence, arguments, . . .

- Operator type compatibility

- Attribute allowance

- Additional type complexity: inference, polymorphism, . . .

# Semantic Analysis: Scope Checking with AST Walking

- Idea: walk through AST (in DFS-order) and validate on the way

- Keep track of scope with declared variables

- ▶  $Scope = (Map[Name \rightarrow Type] names, Scope parent)$

- Might need to keep track of defined types separately

- For identifiers: check existence and get type

- ► For expressions: check types and derive result type

- ► For assignment: check Ivalue-ness of left side

- Might be possible during AST creation

- Needs care with built-ins and other special constructs

# Semantic Analysis and Post-Parsing Transformations

- ► Check for error-prone code patterns

- ▶ Completeness of switch, out-of-range constants, unused variables, ...

- Check method calls, parameter types

- Duplicate code for templates

- ► Make implicit value conversions explicit

- Handle attributes: visibility, warnings, etc.

- ▶ Mangle names, split functions (OpenMP), ABI-specific setup, ...

- ► Last step: generate IR code

# Parsing Performance

#### Is parsing/front-end performance important?

- ► Not necessarily: normal compilers

- ► Some languages (e.g., Rust) need unbounded time for parsing

- ► Somewhat: JIT compilers

- ► Start-up time is generally noticable

- Somewhat more: Developer tools

- Imagine: waiting for seconds just for updated syntax highlighting

- Often uses tricks like incremental updates to parse tree

### Data Types

- ▶ Important part of programming languages

- Might have large variety and compatibility

- Numbers, Strings, Arrays, Compound Types (struct/union), Enum, Templates, Functions, Pointers, . . .

- ► Class hierarchy, Interfaces, Abstract Classes, . . .

- ▶ Integer/float compatibility, promotion, . . .

- Might have implicit conversions

# Data Types: Implementing Classes

- ► Simple class/struct: trivial, just bunch of fields

- Methods take (pointer to) this as implicit parameter

- ► Single inheritance: also trivial extend struct at end

- ▶ Virtual methods: store vtable in object representation

- vtable = table of function pointers for virtual methods

- ► Each sub-class has their own vtable

- Multiple inheritance: embed all parents, multiple vtables

- Dynamic casts: needs run-time type information (RTTI)

#### Recommended Lectures

AD IN2227 "Compiler Constructions" covers parsing/analysis in depth

AD CIT3230000 "Programming Languages" covers dispatching/mixins/...

#### Interpretation on the AST

- 1. Find entry point

- 2. Walk through AST

- Compute values for expressions

- ► Track values of variables in scope

- 3. Profit!

### Compiler Front-end – Summary

- Lexer splits input into tokens

- ► Essentially Regex-Matching + Keywords; rather simple

- ▶ Parser constructs (abstract) syntax tree from tokens

- Top-down vs. bottom-up parsing

- ► Typical: top-down for control flow; bottom-up for expressions

- Respect precedence and associativity for operators

- Semantic analysis ensures meaningful program

- Some data structures are complex to implement

- Some programming languages are more difficult to parse

### Compiler Front-end – Questions

- ▶ What are typical components of a compiler front-end?

- What output does the lexer produce?

- How does a parser disambiguate rules?

- What is the typical way to handle operator precedence?

- Why are not all programming languages describable using CFGs?

- How to implement classes with virtual functions?

# Code Generation for Data Processing

Lecture 3: Intermediate Representations

#### Alexis Engelke

Chair of Data Science and Engineering (125) School of Computation, Information, and Technology Technical University of Munich

Winter 2022/23

### Intermediate Representations: Motivation

- ► So far: program parsed into AST

- + Great for language-related checks

- + Easy to correlate with original source code (e.g., errors)

- Hard for analyses/optimizations due to high complexity

- variable names, control flow constructs, etc.

- Data and control flow implicit

- Highly language-specific

### Intermediate Representations: Motivation

Question: how to optimize? Is x+1 redundant? → hard to tell ∴

### Intermediate Representations: Motivation

Question: how to optimize? Is x+1 redundant? → No! ::

#### Intermediate Representations

- Definitive program representation inside compiler

- During compilation, only the (current) IR is considered

- ► Goal: simplify analyses/transformations

- Technically, single-step compilation is possible for, e.g., C

but optimizations are hard without proper IRs

- Compilers design IRs to support frequent operations

- ► IR design can vary strongly between compilers

- Typically based on graphs or linear instructions (or both)

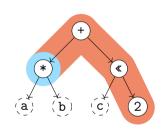

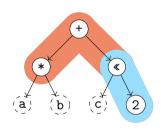

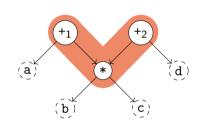

# Graph IRs: Abstract Syntax Tree (AST)

- Code representation close to the source

- Representation of types, constants, etc. might differ

- Storage might be problematic for large inputs

# Graph IRs: Control Flow Graph (CFG)

- Motivation: model control flow between different code sections

- ► Graph nodes represent basic blocks

- ▶ Basic block: sequence of branch-free code (modulo exceptions)

- ► Typically represented using a linear IR

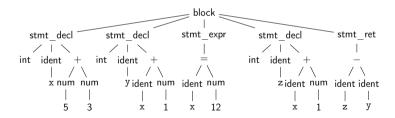

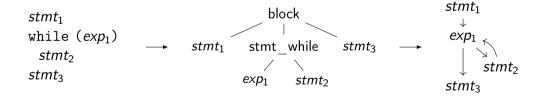

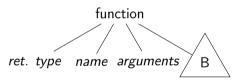

## Build CFG from AST – Function

▶ Idea: Keep track of current insert block while walking through AST

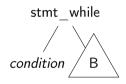

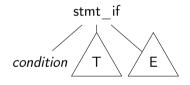

## Build CFG from AST – While Loop

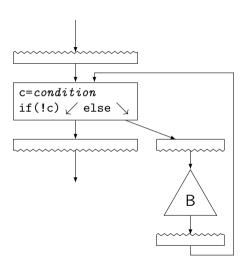

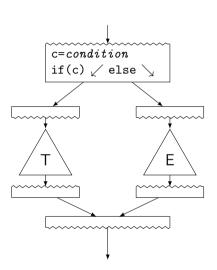

## Build CFG from AST - If Condition

#### Build CFG from AST: Switch

#### Linear search

```

t \leftarrow \exp

if t == 3: goto B_3

if t == 4: goto B_4

if t == 7: goto B_7

if t == 9: goto B_9

goto B_D

```

- + Trivial

- Slow, lot of code

#### Binary search

```

t \leftarrow \exp

if t == 7: goto B_7

elif t > 7:

if t == 9: goto B_9

else:

if t == 3: goto B_3

if t == 4: goto B_4

goto B_D

```

- + Good: sparse values

- Even more code

#### Jump table

```

t \leftarrow \exp

if 0 \le t < 10:

goto table[t]

goto B_D

table = {

B_D, B_D, B_D, B_3, B_4, B_D, \dots}

```

- + Fastest

- Table can be large, needs ind. jump

## Build CFG from AST: Break, Continue, Goto

- break/continue: trivial

- ► Keep track of target block, insert branch

- goto: also trivial

- Split block at target label, if needed

- But: may lead to irreducible control flow graph

#### CFG: Formal Definition

- ▶ Flow graph: G = (N, E, s) with a digraph (N, E) and entry  $s \in N$

- Each node is a basic block, s is the entry block

- $ightharpoonup (n_1, n_2) \in E$  iff  $n_2$  might be executed immediately after  $n_1$

- ▶ All  $n \in N$  shall be reachable from s (unreachable nodes can be discarded)

- Nodes without successors are end points

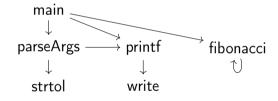

# Graph IRs: Call Graph

- Graph showing (possible) call relations between functions

- Useful for interprocedural optimizations

- Function ordering

- Stack depth estimation

- ...

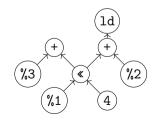

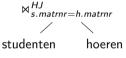

## Graph IRs: Relational Algebra

- ► Higher-level representation of query plans

- Explicit data flow

- ▶ Allow for optimization and selection actual implementations

- ► Elimination of common sub-trees

- Joins: ordering, implementation, etc.

SELECT s.name, h.vorlnr FROM studenten s, hoeren h WHERE s.matrnr = h.matrnr

## Linear IRs: Stack Machines

- Operands stored on a stack

- Operations pop arguments from top and push result

- Typically accompanied with variable storage

- ► Generating IR from AST: trivial

- ▶ Often used for bytecode, e.g. Java, Python

- + Compact code, easy to generate and implement

- Performance, hard to analyze

push 5 push 3 add pop x push x push 1 add pop y push 12 pop x push x push 1 add pop z

## Linear IRs: Register Machines

- Operands stored in registers

- Operations read and write registers

- Typically: infinite number of registers

- ► Typically: three-address form

- ightharpoonup dst = src1 op src2

- Generating IR from AST: trivial

- ► E.g., GIMPLE, eBPF, Assembly

## Example: High GIMPLE

```

int fac (int n)

gimple_bind < // <-- still has lexical scopes</pre>

int D.1950:

int res;

int foo(int n) {

int res = 1:

gimple_assign <integer_cst, res, 1, NULL, NULL>

gimple_goto <<D.1947>>

while (n) {

gimple label << D.1948>>

res *= n * n:

gimple_assign <mult_expr, _1, n, n, NULL>

n = 1:

gimple_assign <mult_expr, res, res, _1, NULL>

gimple_assign <plus_expr, n, n, -1, NULL>

gimple_label <<D.1947>>

return res;

gimple_cond <ne_expr, n, 0, <D.1948>, <D.1946>>

gimple_label <<D.1946>>

gimple_assign <var_decl, D.1950, res, NULL, NULL>

gimple_return <D.1950>

$ gcc -fdump-tree-gimple-raw -c foo.c

```

## Example: Low GIMPLE

```

int fac (int n)

int res:

int D.1950;

int foo(int n) {

gimple_assign <integer_cst, res, 1, NULL, NULL>

int res = 1;

gimple_goto <<D.1947>>

gimple_label <<D.1948>>

while (n) {

gimple_assign <mult_expr, _1, n, n, NULL>

res *= n * n;

gimple_assign <mult_expr, res, res, _1, NULL>

n = 1:

gimple_assign <plus_expr, n, n, -1, NULL>

gimple_label <<D.1947>>

gimple_cond <ne_expr, n, 0, <D.1948>, <D.1946>>

return res:

gimple_label <<D.1946>>

gimple_assign <var_decl, D.1950, res, NULL, NULL>

gimple_goto <<D.1951>>

gimple_label <<D.1951>>

gimple_return <D.1950>

$ gcc -fdump-tree-lower-raw -c foo.c

```

## Example: Low GIMPLE with CFG

```

int fac (int n) {

int res:

int D.1950:

\langle hh 2 \rangle .

gimple_assign <integer_cst, res, 1, NULL, NULL>

goto <bb 4>; [INV]

int foo(int n) {

<bb >3> :

int res = 1:

gimple_assign <mult_expr, _1, n, n, NULL>

gimple_assign <mult_expr, res, res, _1, NULL>

while (n) {

gimple_assign <plus_expr, n, n, -1, NULL>

res *= n * n:

\langle bb | 4 \rangle:

n = 1:

gimple_cond <ne_expr, n, 0, NULL, NULL>

goto <bb 3>; [INV]

else

return res;

goto <bb 5>: [INV]

<bb >5> :

gimple_assign <var_decl, D.1950, res, NULL, NULL>

<bb 6>:

gimple_label <<L3>>

gimple_return <D.1950>

```

\$ gcc -fdump-tree-cfg-raw -c foo.c

## Linear IRs: Register Machines

- ▶ Problem: no clear def—use information

- $\triangleright$  Is x+1 the same?

- ► Hard to track actual values!

- ► How to optimize?

- ⇒ Disallow mutations of variables

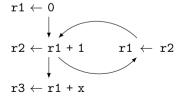

## Single Static Assignment: Introduction

- ▶ Idea: disallow mutations of variables, value set in declaration

- ▶ Instead: create new variable for updated value

- ► SSA form: every computed value has a unique definition

- ► Equivalent formulation: each name describes result of one operation

## Single Static Assignment: Control Flow

- How to handle diverging values in control flow?

- Solution: Φ-nodes to merge values depending on predecessor

- ► Value depends on edge used to enter the block

- All Φ-nodes of a block execute concurrently (ordering irrelevant)

```

entry: x \leftarrow \dots

if (x > 2) goto cont

then: x \leftarrow x * 2

cont: return x

entry: v_1 \leftarrow \dots

if (v_1 > 2) goto cont

then: v_2 \leftarrow v_1 * 2

cont: v_3 \leftarrow \Phi(\text{entry}: v_1, \text{then}: v_2)

return v_3

```

## Example: GIMPLE in SSA form

```

int fac (int n) { int res, D.1950, _1, _6;

\langle bb 2 \rangle:

gimple_assign <integer_cst, res_4, 1, NULL, NULL>

goto <bb 4>; [INV]

\langle bb 3 \rangle:

gimple_assign <mult_expr, _1, n_2, n_2, NULL>

int foo(int n) {

gimple_assign <mult_expr, res_8, res_3, _1, NULL>

int res = 1:

gimple_assign <plus_expr, n_9, n_2, -1, NULL>

<bb 4> :

while (n) {

# gimple_phi < n_2, n_5(D)(2), n_9(3) >

res *= n * n:

# gimple_phi <res_3, res_4(2), res_8(3)>

n = 1:

gimple_cond <ne_expr, n_2, 0, NULL, NULL>

goto <bb 3>: [INV]

else

return res;

goto <bb 5>: [INV]

<bb >5> :

gimple_assign <ssa_name, _6, res_3, NULL, NULL>

<bb 6>:

gimple_label <<L3>>

gimple_return <_6>

```

\$ gcc -fdump-tree-ssa-raw -c foo.c

## SSA Construction – Local Value Numbering

► Simple case: inside block – keep mapping of variable to value

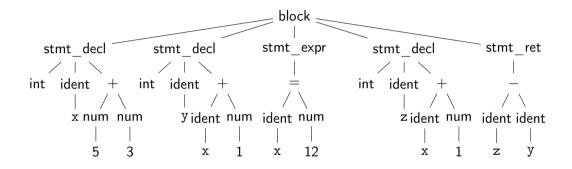

| Code | SSA IR                               |                                                                       |              |         |   |                                  |                                                        |                                                                             | Variable Mapping |                                                                                                        |                                  |  |

|------|--------------------------------------|-----------------------------------------------------------------------|--------------|---------|---|----------------------------------|--------------------------------------------------------|-----------------------------------------------------------------------------|------------------|--------------------------------------------------------------------------------------------------------|----------------------------------|--|

|      | x<br>y<br>x<br>z<br>tmp <sub>1</sub> | $\begin{array}{c} \leftarrow \\ \leftarrow \\ \leftarrow \end{array}$ | x<br>12<br>x | +       | 1 | V <sub>2</sub><br>V <sub>3</sub> | $\leftarrow \\ \leftarrow \\ \leftarrow \\ \leftarrow$ | add 5, 3<br>add $v_1$ , 1<br>const 12<br>add $v_3$ , 1<br>sub $v_4$ , $v_2$ | У                | $\begin{array}{c} \rightarrow \\ \rightarrow \\ \rightarrow \\ \rightarrow \\ \rightarrow \end{array}$ | v <sub>2</sub><br>v <sub>4</sub> |  |

|      | return                               |                                                                       |              | $tmp_1$ |   |                                  |                                                        | ret <i>v</i> s                                                              |                  |                                                                                                        |                                  |  |

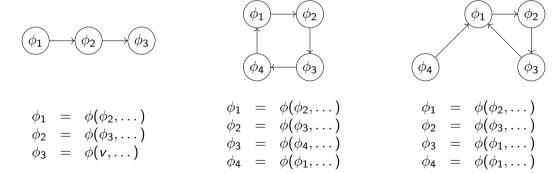

#### SSA Construction – Across Blocks

- SSA construction with control flow is non-trivial

- Key problem: find value for variable in predecessor

- Naive approach: Φ-nodes for all variables everywhere

- Create empty Φ-nodes for variables, populate variable mapping

- Fill blocks (as on last slide)

- Fill Φ-nodes with last value of variable in predecessor

- Why is this a bad idea?

$\Rightarrow$  don't do this!

Extremely inefficient, code size explosion, many dead Φ

# SSA Construction – Across Blocks ("simple" <sup>4</sup>)

- Key problem: find value in predecessor

- ▶ Idea: seal block once all direct predecessors are known

- For acyclic constructs: trivial

- ► For loops: seal header once loop block is generated

- Current block not sealed: add Φ-node, fill on sealing

- Single predecessor: recursively query that

- Multiple preds.: add Φ-node, fill now

## SSA Construction – Example

```

func foo(v_1)

entry:

sealed; varmap: n \rightarrow v_1, res\rightarrow v_2

v_2 \leftarrow 1

header:

sealed: varmap: n \rightarrow \phi_1, res\rightarrow \phi_2

\phi_1 \leftarrow \phi(\text{entry: } v_1, \text{body: } v_6)

int foo(int n) {

\phi_2 \leftarrow \phi(\text{entry: } v_2, \text{body: } v_5)

int res = 1:

v_3 \leftarrow \text{equal } \phi_1, 0

while (n) {

br v_3, cont, body

res *= n * n;

n = 1:

bodv:

sealed: varmap: n \rightarrow v_6, res\rightarrow v_5

v_4 \leftarrow \text{mul } \phi_1, \phi_1

return res:

v_5 \leftarrow \text{mul } \phi_2, v_4

v_6 \leftarrow \text{sub } \phi_1. 1

br header

cont:

sealed; varmap: res\rightarrow \phi_2

ret \phi_2

```

## SSA Construction – Pruned/Minimal Form

- ightharpoonup Resulting SSA is *pruned* all  $\phi$  are used

- ightharpoonup But not minimal  $\phi$  nodes might have single, unique value

- $\blacktriangleright$  When filling  $\phi$ , check that multiple real values exist

- ightharpoonup Otherwise: replace  $\phi$  with the single value

- lacktriangle On replacement, update all  $\phi$  using this value, they might be trivial now, too

- ► Sufficient? Not for irreducible CFG

- ▶ Needs more complex algorithms<sup>5</sup> or different construction method<sup>6</sup>

AD IN2053 "Program Optimization" covers this more formally

<sup>&</sup>lt;sup>5</sup>M Braun et al. "Simple and efficient construction of static single assignment form". In: CC. 2013, pp. 102–122. 🚱.

<sup>&</sup>lt;sup>6</sup>R Cytron et al. "Efficiently computing static single assignment form and the control dependence graph". In: TOPLAS 13.4 (1991), pp. 451–490.

## SSA: Implementation

- Value is often just a pointer to instruction

- $ightharpoonup \phi$  nodes placed at beginning of block

- ► They execute "concurrently" and on the edges, after all

- $\blacktriangleright$  Variable number of operands required for  $\phi$  nodes

- Storage format for instructions and basic blocks

- Consecutive in memory: hard to modify/traverse

- Array of pointers:  $\mathcal{O}(n)$  for a single insertion...

- ► Linked List: easy to insert, but pointer overhead

# Is SSA a graph IR?

Only if instructions have no side effects, consider load, store, call, ...

These can be solved using explicit dependencies as SSA values, e.g. for memory

## Intermediate Representations – Summary

- ► An IR is an internal representation of a program

- Main goal: simplify analyses and transformations

- ▶ IRs typically based on graphs or linear instructions

- ► Graph IRs: AST, Control Flow Graph, Relational Algebra

- Linear IRs: stack machines, register machines, SSA

- Single Static Assignment makes data flow explicit

- SSA is extremely popular, although non-trivial to construct

## Intermediate Representations – Questions

- Who designs an IR? What are design criteria?

- Why is an AST not suited for program optimization?

- How to convert an AST to another IR?

- What are the benefits/drawbacks of stack/register machines?

- What benefits does SSA offer over a normal register machine?

- ▶ How do  $\phi$ -instructions differ from normal instructions?

# Code Generation for Data Processing Lecture 4: LLVM and IR Design

#### Alexis Engelke

Chair of Data Science and Engineering (125) School of Computation, Information, and Technology Technical University of Munich

Winter 2022/23

## LLVM<sup>7</sup>

#### LLVM "Core" Library

- Optimizer and compiler back-end

- "Set of compiler components"

- ► IRs: LLVM-IR, SelDag, MIR

- Analyses and Optimizations

- Code generation back-ends

- Started from Chris Lattner's master's thesis

- ► Used for C, C++, Swift, D, Julia, Rust, Haskell, . . .

#### **LLVM Project**

- Umbrella for several projects related to compilers/toolchain

- LLVM Core

- ► Clang: C/C++ front-end for LLVM

- libc++, compiler-rt: runtime support

- LLDB: debugger

- LLD: linker

- MLIR: experimental IR framework

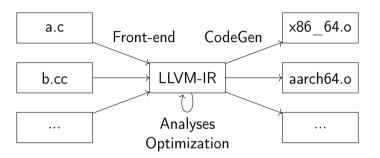

#### LLVM: Overview

- ▶ Independent front-end derives LLVM-IR, LLVM does opt. and code gen.

- ▶ LTO: dump LLVM-IR into object file, optimize at link-time

#### LLVM-IR: Overview

- SSA-based IR, representations textual, bitcode, in-memory

- Hierarchical structure

- Module

- Functions, global variables

- ► Basic blocks

- Instructions

- Strongly/strictly typed

```

define dso_local i32 @foo(i32 %0) {

%2 = icmp eq i32 %0, 0

br i1 %2, label %10, label %3

3: ; preds = %1, %3

%4 = phi i32 [ %7, %3 ], [ 1, %1 ]

\%5 = phi i32 [ \%8, \%3 ], [ \%0, \%1 ]

\%6 = \text{mul nsw i32 } \%5, \%5

%7 = \text{mul nsw i32 } \%6, \%4

\%8 = add nsw i32 \%5, -1

\%9 = icmp eq i32 \%8, 0

br i1 %9, label %10, label %3

10: ; preds = \frac{1}{3}, \frac{1}{1}

%11 = phi i32 [ 1, %1 ], [ %7, %3 ]

ret i32 %11

```

## LLVM-IR: Data types

- First class types:

- ► i<N> arbitrary bit width integer, e.g. i1, i25, i1942652

- ptr/ptr addrspace(1) pointer with optional address space

- ▶ float/double/half/bfloat/fp128/...

- ► <N x ty> vector type, e.g. <4 x i32>

- Aggregate types:

- ► [N x ty] constant-size array type, e.g. [32 x float]

- ▶ { ty, ... } struct (can be packed/opaque), e.g. {i32, float}

- Other types:

- ▶ ty (ty, ...) function type, e.g. {i32, i32} (ptr, ...)

- void

- ► label/token/metadata

## LLVM-IR: Modules

- ► Top-level entity, one compilation unit akin to C/C++

- Contains global values, specified with linkage type

- ► Global variable declarations/definitions

```

@externInt = external global i32, align 4

@globVar = global i32 4, align 4

@staticPtr = internal global ptr null, align 8

```

► Function declarations/definitions

```

declare i32 @readPtr(ptr)

define i32 @return1() {

ret i32 1

}

```

Global named metadata (discarded during compilation)

#### LLVM-IR: Functions

- ► Functions definitions contain all code, not nestable

- Single return type (or void), multiple parameters, list of basic blocks

- ► No basic blocks ⇒ function declaration

- ► Specifiers for callconv, section name, other attributes

- ► E.g.: noinline/alwaysinline, noreturn, readonly

- ▶ Parameter and return can also have attributes

- ► E.g.: noalias, nonnull, sret(<ty>)

#### LLVM-IR: Basic Block

- Sequence of instructions

- $ightharpoonup \phi$  nodes come first

- ► Regular instructions come next

- Must end with a terminator

- First block in function is entry block

Entry block cannot be branch target

#### LLVM-IR: Instructions – Control Flow and Terminators

- Terminators end a block/modify control flow

- ret <ty> <val>/ret void

- ▶ br label <dest>/br i1 <cond>, label <then>, label <else>

- switch/indirectbr

- unreachable

- Few others for exception handling

- ► Not a terminator: call

#### LLVM-IR: Instructions – Arithmetic-Logical

- add/sub/mul/udiv/sdiv/urem/srem

- ► Arithmetic uses two's complement

- ▶ Division corner cases are undefined behavior

- fneg/fadd/fsub/fmul/fdiv/frem

- shl/lshr/ashr/and/or/xor

- Out-of-range shifts have an undefined result

- icmp <pred>/fcmp <pred>/select <cond>, <then>, <else>

- trunc/zext/sext/fptrunc/fpext/fptoui/fptosi/uitofp/sitofp

- bitcast

- Cast between equi-sized datatypes by reinterpreting bits

## LLVM-IR: Instructions – Memory and Pointer

- ► alloca <ty> allocate addressable stack slot

- ▶ load <ty>, ptr <ptr>/store <ty> <val>, ptr <ptr>

- May be volatile (e.g., MMIO) and/or atomic

- cmpxchg/atomicrmw similar to hardware operations

- ptrtoint/inttoptr

- ► Changes provenance! inttoptr(ptrtoint(%x)) is not equal to %x

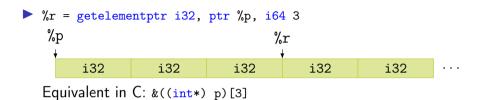

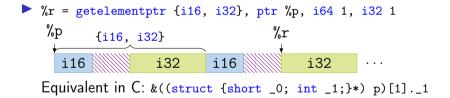

- getelementptr address computation on ptr/structs/arrays

# LLVM-IR: getelementptr Examples

Also works with nested structs and arrays

## LLVM-IR: undef and poison

- undef unspecified value, compiler may choose any value

- $\blacktriangleright$  %b = add i32 %a, i32 undef  $\rightarrow$  i32 undef

- ightharpoonup %c = and i32 %a, i32 undef ightarrow i32 %a

- ightharpoonup %d = xor i32 %b, i32 %b ightarrow i32 undef

- lacktriangle br i1 undef, label %p, label %q ightarrow undefined behavior

- poison result of erroneous operations

- Delay undefined behavior on illegal operation until actually relevant

- ► Allows to speculatively "execute" instructions in IR

- $\blacktriangleright$  %d = shl i32 %b, i32 34  $\rightarrow$  i32 poison

#### LLVM-IR: Intrinsics

- Not all operations provided as instructions

- Intrinsic functions: special functions with defined semantics

- Replaced during compilation, e.g., with instruction or lib call

- ▶ Benefit: no changes needed for parser/bitcode/... on addition

- Examples:

- declare iN @llvm.ctpop.iN(iN <src>)

- declare {iN, i1} @llvm.sadd.with.overflow.iN(iN %a, iN %b)

- memcpy, memset, sqrt, returnaddress, ...

#### LLVM-IR: Tools

- clang can emit LLVM-IR bitcode

clang -0 -emit-llvm -c test.c -o test.bc

- ▶ llvm-dis disassembles bitcode to textual LLVM-IR clang -0 -emit-llvm -c test.c -o - | llvm-dis

- ▶ 11c compiles LLVM-IR (textual or bitcode) to assembly clang -0 -emit-llvm -c test.c -o - | 11c clang -0 -emit-llvm -c test.c -o - | 11vm-dis | 11c

Example Listings omitted – they would span several slides

```

define dso_local <4 x float> @foo2(<4 x float> %0, <4 x float> %1) {

%3 = alloca <4 x float>, align 16

%4 = alloca <4 x float>, align 16

store <4 x float> %0, ptr %3, align 16

store <4 x float> %1, ptr %4, align 16

%5 = load <4 x float>, ptr %3, align 16

%6 = load <4 x float>, ptr %4, align 16

%7 = fadd <4 x float> %5, %6

ret <4 x float> %7

}

```

```

define dso_local i32 @foo3(i32 %0, i32 %1) {

%3 = tail call { i32, i1 } @llvm.smul.with.overflow.i32(i32 %0, i32 %1)

%4 = extractvalue { i32, i1 } %3, 1

%5 = extractvalue { i32, i1 } %3, 0

%6 = select i1 %4, i32 -2147483648, i32 %5

ret i32 %6

}

```

```

define dso_local i32 @sw(i32 %0) {

switch i32 %0, label %4 [

i32 4, label %5

i32 5, label %2

i32 8, label %3

i32 100, label %5

2: : preds = %1

br label %5

3: ; preds = %1

br label %5

4: ; preds = %1

br label %5

5: ; preds = %1, %1, %4, %3, %2

%6 = phi i32 [ %0, %4 ], [ 9, %3 ], [ 32, %2 ], [ 12, %1 ], [ 12, %1 ]

ret i32 %6

```

```

@switch.table.sw = private unnamed_addr constant [7 x i32] [i32 12, i32 32, i32 12,

i32 12, i32 9, i32 12, i32 12], align 4

define dso_local i32 @sw(i32 %0) {

\frac{1}{2} = add i32 \( \frac{1}{2} \), -4

%3 = icmp ult i32 %2, 7

br i1 %3, label %4, label %13

4: : preds = %1

\%5 = trunc i32 \%2 to i8

\%6 = 1 shr i8 83, \%5

\%7 = \text{and i8 } \%6.1

\%8 = icmp eq i8 \%7, 0

br i1 %8, label %13, label %9

9: : preds = %4

%10 = \text{sext } i32 \%2 \text{ to } i64

%11 = getelementptr inbounds [7 x i32], ptr @switch.table.sw, i64 0, i64 %10

%12 = load i32, ptr %11, align 4

br label %13

13: ; preds = %1, %4, %9

%14 = phi i32 [ %12, %9 ], [ %0, %4 ], [ %0, %1 ]

ret i32 %14

```

#### LLVM-IR API

- ► LLVM offers two APIs: C++ and C

- ► C++ is the full API, exposing nearly all internals

- ► C API is more limited, but more stable

- Nearly all major versions have breaking changes

- ► Some support for multi-threading:

- ► All modules/types/... associated with an LLVMContext

- ▶ Different contexts may be used in different threads

## LLVM-IR C++ API: Basic Example

```

#include <11vm/IR/IRBuilder.h>

int main(void) {

llvm::LLVMContext ctx;

auto modUP = std::make_unique<llvm::Module>("mod", ctx);

llvm::Type* i64 = llvm::Type::getInt64Ty(ctx);

llvm::FunctionType* fnTy = llvm::FunctionType::get(i64, {i64}, false);

llvm::Function* fn = llvm::Function::Create(fnTv.

11vm::GlobalValue::ExternalLinkage, "addOne", modUP.get());

llvm::BasicBlock* entryBB = llvm::BasicBlock::Create(ctx, "entry", fn);

llvm::IRBuilder<> irb(entryBB);

llvm::Value* add = irb.CreateAdd(fn->getArg(0), irb.getInt64(1));

irb.CreateRet(add);

modUP->print(llvm::outs(), nullptr);

return 0:

```

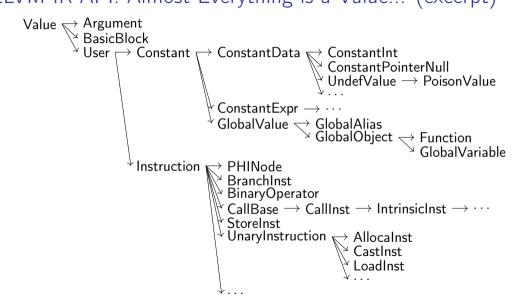

# LLVM-IR API: Almost Everything is a Value... (excerpt)

#### LLVM-IR API: Programming Environment

- LLVM implements custom RTTI

- isa<>, cast<>, dyn\_cast<>

- LLVM implements a multitude of specialized data structures

- ► E.g.: SmallVector<T, N> to keep N elements stack-allocated

- ► Custom vectors, sets, maps; see manual<sup>8</sup>

- Preferably uses ArrayRef, StringRef, Twine for references

- ▶ LLVM implements custom streams instead of std streams

- outs(), errs(), dbgs()

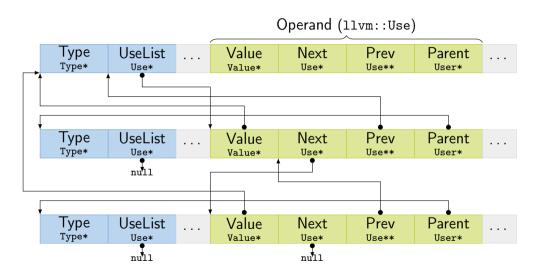

### LLVM-IR API: Use Tracking

Values track their users

```

llvm::Value* v = /* ... */;

for (llvm::User* u : v->users())

if (auto i = llvm::dyn_cast<llvm::Instruction>(u))

// ...

```

- Simplifies implementation of analyses

- ► Allows for easy replacement:

- inst->replaceAllUsesWith(replVal);

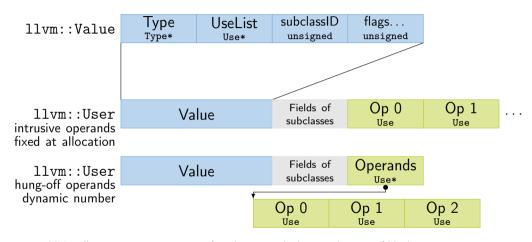

## LLVM IR Implementation: Value/User

PHINode additionally stores n BasicBlock\* after the operands, but aren't users of blocks.

#### LLVM IR Implementation: Use

## LLVM IR Implementation: Instructions/Blocks

- Instruction and BasicBlock have pointers to parent and next/prev

- Linked list updated on changes and used for iteration

- Instructions have cached order (integer) for fast "comes before"

- ▶ BasicBlock successors: blocks used by terminator

- BasicBlock predecessors:

- Iterate over users of block these are terminators (and blockaddress)

- ▶ Ignore non-terminators, parent of using terminator is predecessor

- ▶ Same predecessor might be duplicated (~> getUniquePredecessor())

- Finding first non- $\phi$  requires iterating over  $\phi$ -nodes

#### LLVM and IR Design

- ► LLVM provides a decent general-purpose IR for compilers

- But: not ideal for all purposes

- High-level optimizations difficult, e.g. due to lost semantics

- Several low-level operations only exposed as intrinsics

- ► IR rather complex, high code complexity

- High compilation times

- ► Thus: heavy trend towards custom IRs

#### IR Design: High-level Considerations

- Define purpose!

- Structure: SSA vs. something else; control flow

- Control flow: basic blocks/CFG vs. structured control flow

- Remember: SSA can be considered as a DAG, too

- SSA is easy to analyse, but non-trivial to construct/leave

- Broader integration: keep multiple stages in single IR?

- Example: create IR with high-level operations, then incrementally lower

- ► Model machine instructions in same IR?

- Can avoid costly transformations, but adds complexity

### IR Design: Operations

- Data types

- Simple type structure vs. complex/aggregate types?

- ► Keep relation to high-level types vs. low-level only?

- Virtual data types, e.g. for flags/memory?

- Instruction format

- Single vs. multiple results?

- Strongly typed vs. more generic result/operand types?

- ▶ Operand number fixed vs. dynamic?

#### IR Design: Operations

- ► Allow instruction side effects?

- ► E.g.: memory, floating-point arithmetic, implicit control flow

- Operation complexity and abstraction

- ► E.g.: CheckBounds, GetStackPtr, HashInt128

- ► E.g.: load vs. MOVQconstidx4

- Extensibility for new operations (e.g., new targets, high-level ops)

#### IR Design: Implementation

- Maintain user lists?

- Simplifies optimizations, but adds considerable overhead

- ▶ Replacement can use copy and lazy canonicalization

- User count might be sufficient alternative

- Storage layout: operation size and locations

- ► For performance: reduce heap allocations, small data structures

- Special handling for arguments vs. all-instructions?

- ▶ Metadata for source location, register allocation, etc.

- $\triangleright$  SSA:  $\phi$  nodes vs. block arguments?

#### IR Example: Go SSA

- Strongly typed

- Structured types decomposed

- Explicit memory side-effects

- Also High-level operations

- ► IsInBounds, VarDef

- Only one type of value/instruction

- Const64, Arg, Phi

- No user list, but user count

- Also used for arch-specific repr.

env GOSSAFUNC=fac go build test.go

```

b1:

v1 (?) = InitMem < mem >

v2 (?) = SP <uintptr>

v5 (?) = LocalAddr <*int> {~r1} v2 v1

v6 (7) = Arg < int > {n} (n[int])

v8 (?) = Const64 < int > [1] (res[int])

v9 (?) = Const64 <int> [2] (i[int])

Plain -> b2 (+9)

b2: <- b1 b4

v10 (9) = Phi < int > v9 v17 (i[int])

v23 (12) = Phi < int > v8 v15 (res[int])

v12 (+9) = Less64 < bool > v10 v6

If v12 -> b4 b5 (likely) (9)

b4 \cdot < - b2

v15 (+10) = Mul64 <int> v23 v10 (res[int])

v17 (+9) = Add64 < int > v10 v8 (i[int])

Plain -> b2 (9)

b5: <- b2

v20 (12) = VarDef < mem > {^r1} v1

v21 (+12) = Store < mem > {int} v5 v23 v20

Ret v21 (+12)

```

#### LLVM and IR Design – Summary

- LLVM is a modular compiler framework

- Extremely popular and high-quality compiler back-end

- Primarily provides optimizations and a code generator

- Main interface is the SSA-based LLVM-IR

- Easy to generate, friendly for writing front-ends/optimizations

- ► IR design depends on purpose and integration constraints

- Structurally similar IRs can strongly differ in capabilities

#### LLVM and IR Design – Questions

- What is the structure of an LLVM-IR module/function?

- Which LLVM-IR data types exist? How do they relate to the target architecture?

- How do semantically invalid operations in LLVM-IR behave?

- What is special about intrinsic functions?

- How to derive LLVM-IR from C code using Clang?

- How does LLVM's replaceAllUsesWith work? How could this work without building/maintaining user lists?

- ▶ How can an SSA-based IR make side effects explicit?

- ▶ How would you design an IR for optimizing Brainfuck?

# Code Generation for Data Processing

Lecture 5: Analyses and Transformations

#### Alexis Engelke

Chair of Data Science and Engineering (125) School of Computation, Information, and Technology Technical University of Munich

Winter 2022/23

#### Program Transformation: Motivation

- "User code" is often not very efficient

- ► Also: no need to, compiler can (often?) optimize better

- ▶ More knowledge: e.g., data layout, constants after inlining, etc.

- Allows for more pragmatic/simple code

- ► Generating "better" IR code on first attempt is expensive

- What parts are actually used? How to find out?

- ▶ Transformation to "better" code must be done *somewhere*

- ▶ Optimization is a misnomer: we don't know whether it improves code!

- ► Many transformations are driven by heuristics

- ► Many types of optimizations are well-known<sup>9</sup>

#### Dead Block Elimination

- CFG not necessarily connected

- ► E.g., consequence of optimization

- ightharpoonup Conditional branch

- Removing dead blocks is trivial

- 1. DFS traversal of CFG from entry, mark visited blocks

- 2. Remove unmarked blocks

# Optimization Example 1

```

define i32 @fac(i32 %0) {

br label %for.header

for.header: ; preds = %for.body, %1

%a = phi i32 [ 1, %1 ], [ %a.new, %for.body ]

%b = phi i32 [ 0, %1 ], [ %b.new, %for.body ]

%i = phi i32 [ 0, %1 ], [ %i.new, %for.body ]

%cond = icmp sle i32 %i, %0

br i1 %cond, label %for.body, label %exit

for.body: ; preds = %for.header

%a.new = mul i32 %a, %i

\%b.new = add i32 \%b, \%i

\%i.new = add i32 \%i. 1

br label %for.header

exit: ; preds = %for.header

%absum = add i32 %a, %b

ret i32 %a

```

# Simple Dead Code Elimination (DCE)

- Look for trivially dead instructions

- No users or side-effects

- Calls might be removed

- 1. Add all instructions to work queue

- 2. While work queue not empty:

- 2.1 Check for deadness

- 2.2 If dead, remove and add all operands to work queue

Warning: Don't implement it this naively, this is inefficient

# Applying Simple DCE

```

define i32 @fac(i32 %0) {

eff : cf br label %for.header

for.header: ; preds = %for.body, %1

users: 1 %a = phi i32 [ 1, %1 ], [ %a.new, %for.body ]

users: 1 %b = phi i32 [ 0, %1 ], [ %b.new, %for.body ]

users: 4 %i = phi i32 [ 0, %1 ], [ %i.new, %for.body ]

users: 1 \%cond = icmp sle i32 \%i, \%0

eff.: cf br i1 %cond, label %for.body, label %exit

for.body: ; preds = %for.header

users: 1 \%a.new = mul i32 \%a. \%i

users: 1 %b.new = add i32 %b. %i

users: 1 %i.new = add i32 %i, 1

eff cf br label %for.header

exit: ; preds = %for.header

eff.: cf ret i32 %a

```

#### Dead Code Elimination

- Problem: unused value cycles

- ▶ Idea: find "value sinks" and mark all needed values as live unmarked values can be removed

- ➤ Sink: instruction with side effects (e.g., store, control flow)

- 1. Only mark instrs. with side effects as live

- 2. Populate work list with newly added live instrs.

- 3. While work list not empty:

- 3.1 Mark dead operand instructions as live and add to work list

- 4. Remove instructions not marked as live

## Applying Liveness-based DCE

```

Work list (stack)

define i32 @fac(i32 %0) {

live br<sub>1</sub> label %for.header

for.header: ; preds = %for.body, %1

%a = phi i32 [ 1, %1 ], [ %a.new, %for.body ]

live

live

%i = phi i32 [ 0, %1 ], [ %i.new, %for.body ]

live %cond = icmp sle i32 %i, %0

br<sub>2</sub> i1 %cond, label %for.body, label %exit

live

for.body: ; preds = %for.header

live %a.new = mul i32 %a, %i

live %i.new = add i32 %i, 1

br<sub>3</sub> label %for.header

exit: ; preds = %for.header

live

ret i32 %a

}

```

## Optimization Example 2

```

define i32 @foo(i32 %0, ptr %1, ptr %2) {

%4 = zext i32 %0 to i64

%5 = getelementptr inbounds i32, ptr %1, i64 %4

%6 = load i32, ptr %5, align 4

%7 = zext i32 %0 to i64

%8 = getelementptr inbounds i32, ptr %2, i64 %7

%9 = load i32, ptr %8, align 4

%10 = add nsw i32 %6, %9

ret i32 %10

}

```

# Common Subexpression Elimination (CSE) – Attempt 1

- ▶ Idea: find/eliminate redundant computation of same value

- Keep track of previously seen values in hash map

- Iterate over all instructions

- ▶ If found in map, remove and replace references

- Otherwise add to map

- Easy, right?

# CSE Attempt 1 – Example 1

```

define i32 @foo(i32 %0, ptr %1, ptr %2) {

→ ht

→ ht

→ ht

→ ht

%5 = getelementptr inbounds i32, ptr %1, i64 %4

→ ht

dup %4

%7 = zext i32 %0 to i64

→ ht

→ ht

%8 = getelementptr inbounds i32, ptr %2, i64 %7%4

→ ht

→ ht

%9 = load i32, ptr %8, align 4

→ ht

%10 = add nsw i32 %6, %9

ret i32 %10

}

```

Obsolete instr. can be killed immediately, or in a later DCE

## CSE Attempt 1 – Example 2

```

define i32 @square(i32 %a, i32 %b) {

entry:

%cmp = icmp slt i32 %a, %b

\rightarrow ht

\rightarrow ht

br i1 %cmp, label %if.then, label %if.end

if.then: ; preds = %entry

%add1 = add i32 %a, %b

\rightarrow ht

\rightarrow ht

br label %if.end

if.end: ; preds = %if.then, %entry

%condvar = phi i32 [ %add1, %if.then ], [ %a, %entry ]

\rightarrow ht

dup %add1

%add2 = add i32 %a, %b

%res = add i32 %condvar, %add2%add1

\rightarrow ht

\rightarrow ht

ret i32 %res

```

Instruction does not dominate all uses!

error: input module is broken!

#### **Domination**

- ▶ Remember: CFG G = (N, E, s) with digraph (N, E) and entry  $s \in N$

- Dominate: d dom n iff every path from s to n contains d

- ▶ Dominators of n:  $DOM(n) = \{d | d \text{ dom } n\}$

- ▶ Strictly dominate: d sdom  $n \Leftrightarrow d$  dom  $n \land d \neq n$

- ► Immediate dominator: idom (n) = d : d sdom  $n \land \not\exists d'.d$  sdom  $d' \land d'$  sdom n

- ⇒ All strict dominators are always executed before the block

- ⇒ All values from dominators available/usable

- ⇒ All values not from dominators **not** usable

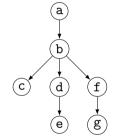

#### Dominator Tree

- ► Tree of immediate dominators

- Allows to iterate over blocks in pre-order/post-order

- ► Answer *a* sdom *b* quickly

# Control Flow Graph Dominator Tree a b b

#### Dominator Tree: Construction

- ► Naive: inefficient (but reasonably simple)<sup>10</sup>

- ► For each block: find a path from the root superset of dominators

- ▶ Remove last block on path and check for alternative path

- If no alternative path exists, last block is idom

- ► Lengauer—Tarjan: more efficient methods<sup>11</sup>

- Simple method in  $\mathcal{O}(m \log n)$ ; sophisticated method in  $\mathcal{O}(m \cdot \alpha(m, n))$  ( $\alpha(m, n)$  is the inverse Ackermann function, grows extremely slowly)

- ► Used frequently in compilers<sup>12</sup>

<sup>10</sup> ES Lowry and CW Medlock. "Object code optimization". In: CACM 12.1 (1969), pp. 13-22.

<sup>11</sup>T Lengauer and RE Tarjan. "A fast algorithm for finding dominators in a flowgraph". In: TOPLAS 1.1 (1979), pp. 121–141. 🚱

<sup>12</sup> Example: https://github.com/WebKit/WebKit/blob/aabfacb/Source/WTF/wtf/Dominators.h

#### Dominator Tree: Implementation

- Per node store: idom, idom-children, DFS pre-order/post-order number

- ► Get immediate dominator: ...lookup idom

- Iterate over all dominators/dominated by: ...trivial

- ightharpoonup Check whether a sdom  $b^{13}$

- ▶ a.preNum < b.preNum ∧ a.postNum > b.postNum

- ▶ After updates, numbers might be invalid: recompute or walk tree

- ▶ Problem: dominance of unreachable blocks ill-defined → special handling

# CSE Attempt 2

- ► Option 1:

- For identical instructions, store all

- Add dominance check before replacing

- ▶ Visit nodes in reverse post-order (i.e., topological order)

- ▶ Option 2:<sup>14</sup>

- Do a DFS over dominator tree

- Use scoped hashmap to track available values

Does this work? Yes

152

# CSE: Hashing an Instruction (and Beyond)

- ▶ Needs hash function and "relaxed" equality

- ▶ Idea: combine opcode and operands/constants into hash value

- Use pointer or index for instruction result operands

- Canonicalize commutative operations

- Order operands deterministically, e.g., by address

- ► Identities: a+(b+c) vs. (a+b)+c

## Global Value Numbering - or: advanced CSE

- ► Hash-based approach only catches trivially removable duplicates

- ► Alternative: partition values into congruence classes

- Congruent values are guaranteed to always have the same value

- ▶ Optimistic approach: values are congruent unless proven otherwise

- ▶ Pessimistic approach: values are not congruent unless proven

- Combinable with: reassociation, DCE, constant folding

- ► Rather complex, but can be highly beneficial<sup>15</sup>

# Simple Transformations: Inlining

- Estimate whether inlining is beneficial

- Savings of avoided call/computations/branches; cost of increased size

- Copy original function in place of the call

- ► Split basic block containing function call

- ightharpoonup Replace returns with branches and  $\phi$ -node to/at continuation point

- Move alloca to beginning or save stack pointer

- Prevent unbounded stack growth in loops

- ► LLVM provides stacksave/stackrestore intrinsics

- Exceptions may need special treatment

# Simple Transformations: Mem2Reg and SROA

- Mem2reg: promote alloca to SSA values/phis

- ► Condition: only load/store, no address taken

- Essentially just SSA construction

- ► SROA: scalar replacement of aggregate

- Separate structure fields into separate variables

- Also promote them to SSA

#### Loops

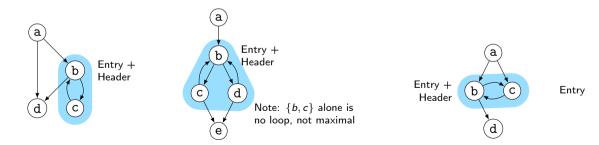

- ► Loop: maximal SCC *L* with at least one internal edge<sup>16</sup> (strongly connected component (SCC): all blocks reachable from each other)

- ► Entry: block with an edge from outside of *L*

- ► Header *h*: first entry found (might be ambiguous)

- ▶ Loop nested in L: loop in subgraph  $L \setminus \{h\}$

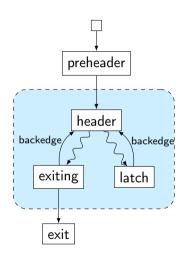

## Natural Loops

- Natural Loop: loop with single entry

- ⇒ Header is unique

- ⇒ Header dominates all block

- ⇒ Loop is reducible

- ► Backedge: edge from block to header

- ▶ Predecessor: block with edge into loop

- ► Preheader: unique predecessor

#### Formal Definition

Loop L is reducible iff  $\exists h \in L : \forall n \in L : h \text{ dom } n$ CFG is reducible iff all loops are reducible

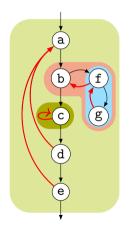

# Finding Natural Loops

- ► Modified version<sup>17</sup> of Tarjan's algorithm<sup>18</sup>

- ▶ Iterate over dominator tree in post order

- Each block: find predecessors dominated by the block

- None → no loop header, continue

- ightharpoonup Any ightharpoonup loop header, these edges must be backedges

- Walk through predecessors until reaching header again

- ► All blocks on the way must be part of the loop body

- Might encounter nested loops, update loop parent

<sup>17</sup>G Ramalingam. "Identifying loops in almost linear time". In: TOPLAS 21.2 (1999), pp. 175–188. 🚱.

<sup>18</sup>R Tarjan. "Testing flow graph reducibility". In: STOC. 1973, pp. 96-107.

# Finding Natural Loops: Example

#### Control Flow Graph

#### Dominator Tree

#### Loop Info

Loop A: {c}

header: c; parent: D

Loop  $B: \{f,g\}$

header: f; parent: C

Loop C: {b,f,g} header: b; parent: D

Loop D: {a,b,c,d,e,f,g}

header: a; parent: NULL

# Loop Invariant Code Motion (LICM)

- Analyze loops, iterate over loop tree in post-order

- ► I.e., visit inner loops first

- ↑ Hoist:<sup>19</sup> iterate over blocks of loop in reverse post-order

- For each movable inst., check for loop-defined operands

- ▶ If not, move to preheader (create one, if not existent)

- ▶ Otherwise, add inst. to set of values defined inside loop

- ↓ Sink: Iterate over blocks of loop in post-order

- For each movable inst., check for users inside loop

- ▶ If none, move to unique exit (if existent)

# Transformations and Analyses in LLVM: Passes

- ► Transformations and analyses organized in *passes*

- ► Pass can operate on Module/(CGSCC)/Function/Loop

- Analysis pass: takes input IR and returns analysis result

- ▶ May also use results of other analyses; results are cached

- ► Transformation pass: takes input IR and returns preserved analyses

- ► Can use analyses, which are re-run when outdated

- Pass manager executes passes on same granularity

- Otherwise, use adaptor: createFunctionToLoopPassAdaptor (and preferably combine multiple smaller passes into a separate pass manager)

# Using LLVM (New) Pass Manager

```

void optimize(llvm::Function* fn) {

llvm::PassBuilder pb;

llvm::LoopAnalysisManager lam{};

llvm::FunctionAnalysisManager fam{};

llvm::CGSCCAnalysisManager cgam{};

llvm::ModuleAnalysisManager mam{};

pb.registerModuleAnalyses(mam);

pb.registerCGSCCAnalyses(cgam);

pb.registerFunctionAnalyses(fam);

pb.registerLoopAnalyses(lam);

pb.crossRegisterProxies(lam, fam, cgam, mam);

llvm::FunctionPassManager fpm{};

fpm.addPass(llvm::DCEPass());

fpm.addPass(11vm::createFunctionToLoopPassAdaptor(11vm::LoopRotatePass()));

fpm.run(*fn, fam);

```

# Writing a Pass for LLVM's New PM – Part 1

```

#include "llvm/IR/PassManager.h"

#include "llvm/Passes/PassBuilder.h"

#include "llvm/Passes/PassPlugin.h"

class TestPass : public llvm::PassInfoMixin<TestPass> {

public:

11vm::PreservedAnalyses run(11vm::Function &F.

llvm::FunctionAnalysisManager &AM) {

// Do some magic

11vm::DominatorTree *DT = &AM.getResult<11vm::DominatorTreeAnalvsis>(F);

// ...

llvm::errs() << F.getName() << "\n";</pre>

return llvm::PreservedAnalyses::all();

```

# Writing a Pass for LLVM's New PM - Part 2

```

extern "C" ::llvm::PassPluginLibraryInfo LLVM_ATTRIBUTE_WEAK

llvmGetPassPluginInfo() {

return { LLVM_PLUGIN_API_VERSION, "TestPass", "v1",

[] (llvm::PassBuilder &PB) {

PB.registerPipelineParsingCallback(

[] (llvm::StringRef Name, llvm::FunctionPassManager &FPM,

llvm::ArrayRef<llvm::PassBuilder::PipelineElement>) {

if (Name == "testpass") {

FPM.addPass(TestPass());

return true:

return false:

}):

} }:

c++ -shared -o testpass.so testpass.cc -lLLVM -fPIC

opt -load-pass-plugin=$PWD/testpass.so -passes=testpass input.ll | llvm-dis

```

# Analyses and Transformations – Summary

- Program Transformation critical for performance improvement

- Code not necessarily better

- Analyses are important to drive transformations

- ▶ Dominator tree, loop detection, value liveness

- Important optimizations

- Dead code elimination, common sub-expression elimination, loop-invariant code motion

- ► Compilers often implement transformations as passes

- Analyses may be invalidated by transformations, needs tracking

## Analyses and Transformations – Questions

- ▶ Why is "optimization" a misleading name for a transformation?

- ▶ How to find unused code sections in a function's CFG?

- Why is a liveness-based DCE better than a simple, user-based DCE?

- ▶ What is a dominator tree useful for?

- ▶ What is the difference between an irreducible and a natural loop?

- How to find natural loops in a CFG?

- How does the algorithm handle irreducible loops?

- Why is sinking a loop-invariant inst. harder than hoisting?

# Code Generation for Data Processing

Lecture 6: Instruction Selection

#### Alexis Engelke

Chair of Data Science and Engineering (125) School of Computation, Information, and Technology Technical University of Munich

Winter 2022/23

#### Code Generation – Overview

- ► Instruction Selection

- Map IR to assembly

- Keep code shape and storage; change operations

- Instruction Scheduling

- Optimize order to hide latencies

- Keep operations, may increases demand for registers

- Register Allocation

- Map virtual to architectural registers and stack

- Adds operations (spilling), changes storage

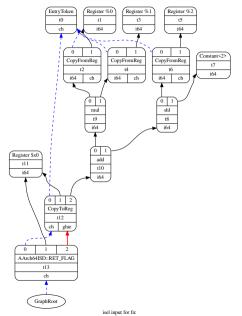

# Instruction Selection (ISel) – Overview

- ► Find machine instructions to implement abstract IR

- Typically separated from scheduling and register allocation

- Input: IR code with abstract instructions

- Output: lower-level IR code with target machine instructions

```

i64 %10 = add %8, %9

i8 %11 = trunc %10

i64 %12 = const 24

i64 %13 = add %7, %12

store %11, %13

i64 %10 = ADD %8, %9

STRB %10, [%7+24]

```

### ISel – Typical Constraints

- Target offers multiple ways to implement operations

- ▶ imul x, 2, add x, x, shl x, 1, lea x, [x+x]

- ► Target operations have more complex semantics

- ► E.g., combine truncation and offset computation into store

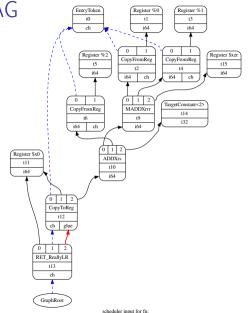

- ► Can have multiple outputs, e.g. value+flags, quotient+remainder